# **Decoupling Capacitors and PCB** Layout: What is Really Important?

**Prof Eric Bogatin**

Eric.Bogatin@colorado.edu

Spring 2023

University of Colorado, Boulder, ECEE

High Speed Digital Engineering Group

About the Eric

**Eric Bogatin** Prof, University of Colorado, Boulder Fellow: Teledyne LeCroy Technical Editor, Signal Integrity Journal

- Physics: BS MIT '76 and PhD U of A Tucson, '80 •

- Senior management and engineering positions at Bell Labs, Raychem, Sun Micro, Ansys, Interconnect Devices Inc

- Started Bogatin Enterprises in 1992, created the Signal Integrity Academy, acquired by LeCroy in 2011. Teledyne LeCroy Fellow

- Full time Prof, ECEE dept University of Colorado, Boulder, since 2021, teaching signal integrity, PCB design, Capstone Senior Design Lab

- Author: 15 books, including popular textbooks and science fiction novels, monthly columns

University of Colorado, Boulder, ECEE

High Speed Digital Engineering Group

### **Other Resources**

### Major Research Programs of the HSDE Group

- Low-Cost Hands-On Demonstrations of SI/PI/EMI Best Design, Simulation, Measurement, Analysis Practices and Pathological Examples (primary audience is course content)

- Low-Cost SI/PI/EMI Technology Solutions (primary audience is engineer)

- Improving **Measurement-Simulation Correlation** of Circuits and Interconnects from 1 Hz to 40 GHz

- Low-Cost Software Defined Instruments

- Challenges in PDN design

- One example: rail collapse for I/O switching

- An homage to Bob Pease

- So what? good and not so good PCB layout strategies

- Legacy Code

- Final recommendations

University of Colorado, Boulder, ECEE

High Speed Digital Engineering Group

**Design is First About Connectivity**

A schematic identifies:

BOM

5

- Functionality

- Connectivity

- Wires are transparent- no R, no delay

The interconnects live in the wires and the white space of the schematic

If the interconnects are transparent, design for performance doesn't apply. It's all about connectivity, DFM, DFR, DFT,...

A layout represents the physical design of the interconnects

...but, in almost every design, they are not transparent

Once connectivity is correct, the only thing interconnects are going to do is screw up the performance The goal in interconnect design is to minimize how much the interconnects screw things up

University of Colorado, Boulder, ECEE

High Speed Digital Engineering Group

### Four Hurdles in PDN Design

- The problem with PDN design is not 1 problem, it is 12 problems

- · Identifying the root cause of each problem is hard

- There are 9 orders of magnitude between low current PDNs (1 uA) and high current PDNs (1000 A). One solution cannot apply to all

- There is a lot of "noise" and "legacy code" circulating in the industry about PDN design

University of Colorado, Boulder, ECEE

High Speed Digital Engineering Group

Watch out for the "streetlight effect": a common origin for PDN design guidelines

"I'm searching for my keys."

The right solution is not always where it's easy to find

University of Colorado, Boulder, ECEE

High Speed Digital Engineering Group

8

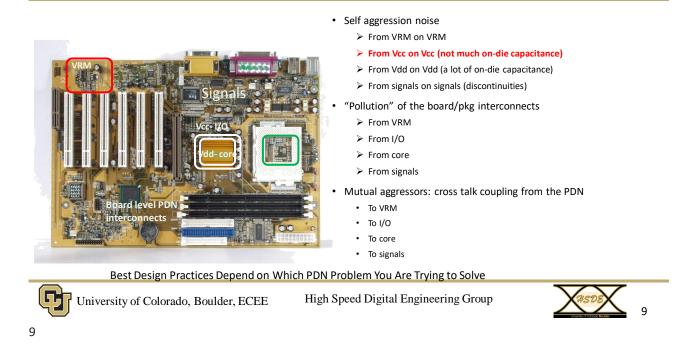

### Why PDN Design is so Confusing: It's not just 1 problem and root cause, it's 12

# Agenda

- Challenges in PDN design

- One example: rail collapse for I/O switching

- An homage to Bob Pease

- So what? good and not so good PCB layout strategies

- Legacy Code

- Final recommendations

University of Colorado, Boulder, ECEE

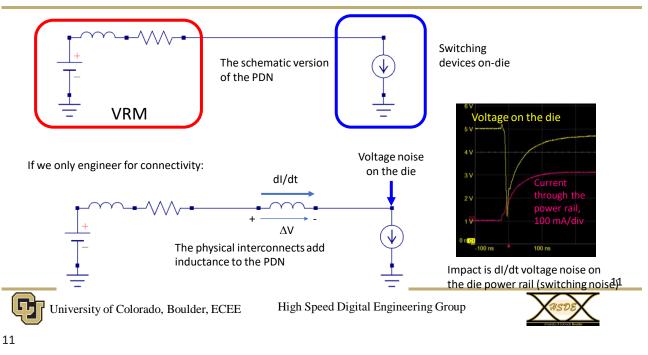

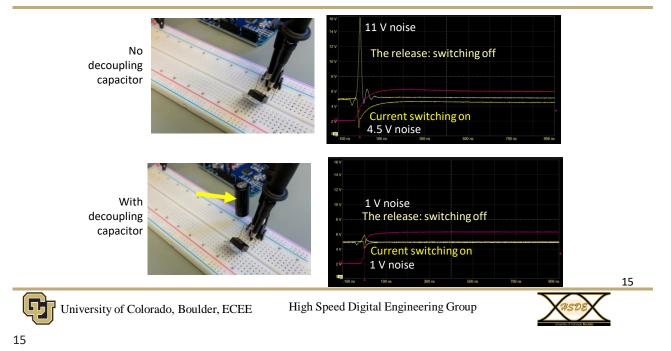

### The Origin of I/O Switching Noise on the Power Rail

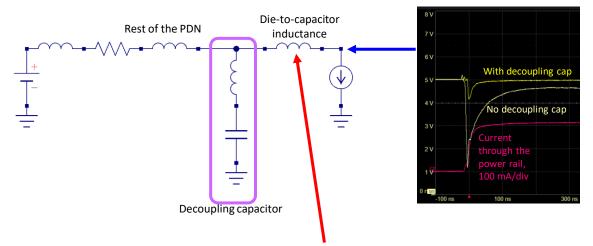

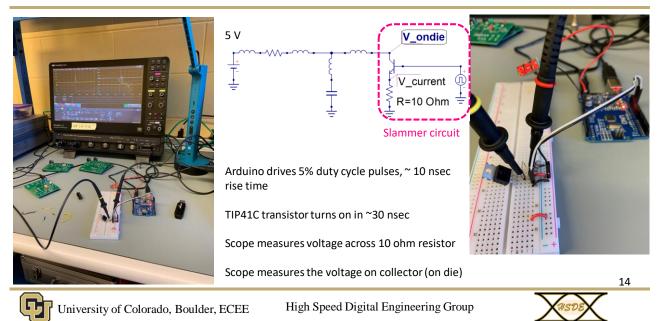

### Reduce Switching Noise by adding Decoupling Capacitors "Decouples" the IC from the Rest of the PDN Inductance

Switching noise on-die is reduced by reducing the Die-to-capacitor inductance

- Challenges in PDN design

- One example: rail collapse for I/O switching

- An homage to Bob Pease

- So what? good and not so good PCB layout strategies

- Legacy Code

- Final recommendations

### An Homage to Bob Pease, "My simulation language is solder"

### The Origin of I/O Switching Noise on the Power Rail

### How Much Capacitance is Enough?

- The purpose of the capacitor is to reduce the inductance the die sees.

- How much capacitance to add?

$$C > \frac{\Delta Q}{\Delta V} = \frac{I\Delta t}{\Delta V} = \frac{0.4A \times 100n \text{ sec}}{0.1V} = 400nF$$

To first order, doesn't matter how much larger the capacitor is- just that it is low inductance

University of Colorado, Boulder, ECEE

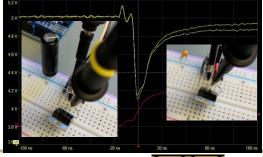

Power rail noise with 1000 uF and 1 uF capacitors

High Speed Digital Engineering Group

- Challenges in PDN design

- One example: rail collapse for I/O switching

- An homage to Bob Pease

- So what? good and not so good PCB layout strategies

- Legacy Code

- Final recommendations

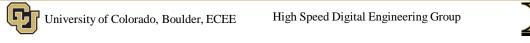

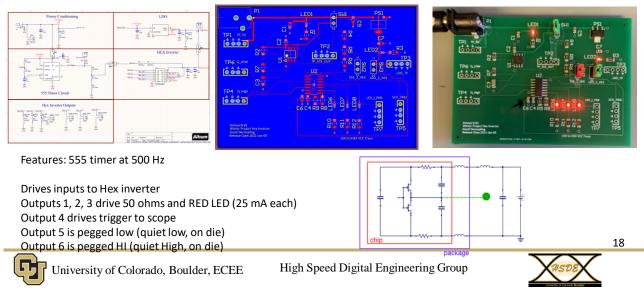

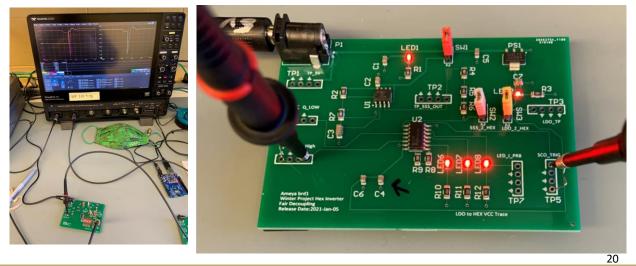

### A Circuit Board Experiment

with my student Ameya Ramadurgakar

### **Three Identical Schematics, Different Layouts**

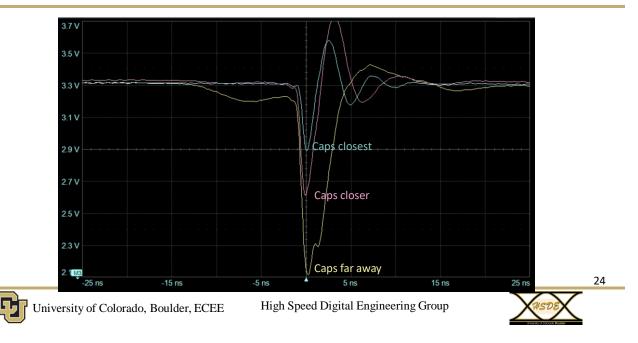

Identical boards. Just differ by placement of the 2 decoupling capacitors for the hex inverter

Boards designed by Ameya Ramadurgakar

### Rule #9: what do we expect?

University of Colorado, Boulder, ECEE High

High Speed Digital Engineering Group

Important Design Principle for Prototypes: Design for Test and Bring Up with 10x Probe Test Points

University of Colorado, Boulder, ECEE

High Speed Digital Engineering Group

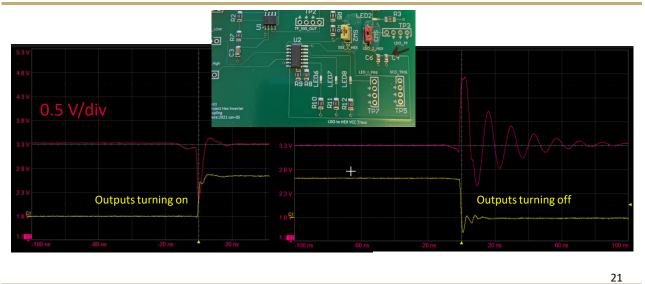

# **Really Bad Routing**

High Speed Digital Engineering Group

21

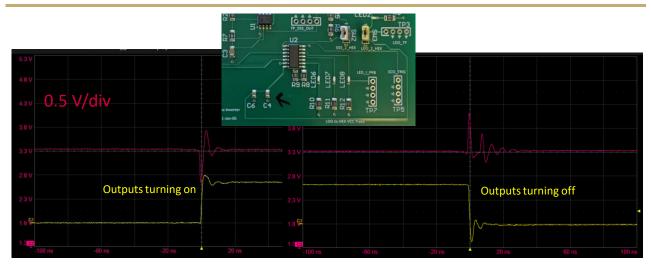

# **Fair Routing**

University of Colorado, Boulder, ECEE

22

High Speed Digital Engineering Group

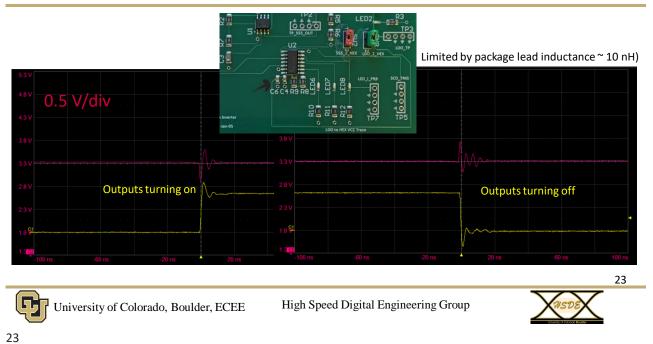

# **Best Routing**

### How the Decoupling Capacitors are Placed, Matters

- Challenges in PDN design

- One example: rail collapse for I/O switching

- An homage to Bob Pease

- So what? good and not so good PCB layout strategies

### • Legacy Code

• Final recommendations

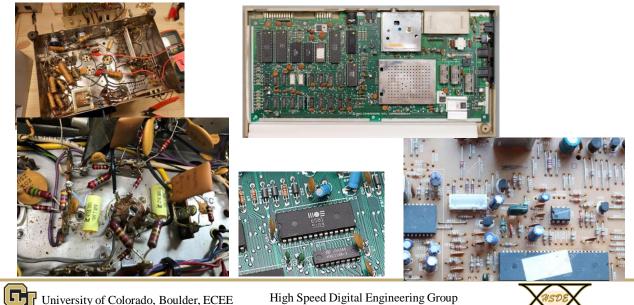

### Historical Driving Force in Reducing Switching Noise: use three different value decoupling capacitors: 10 uF, 1 uF, 0.1 uF

How to achieve low inductance?

Historically:

25

- Smaller capacitance value capacitors were smaller physical size and lower inductance: "High frequency capacitors"

- Use small size capacitors to get low inductance. Add larger size capacitors to get more capacitance.

- The origin of the recommendation: Use three capacitors in parallel: 10 uF, 1 uF, 0.1 uF

: Use three capacitors in

Parallel combination 1E3 1E4 1E5 1E6 1E7 Frequency, Hz

https://www.signalintegrityjournal.com/articles/1589-the-myth-

1E8

1E9

26

University of Colorado, Boulder, ECEE

High Speed Digital Engineering Group

of-three-capacitor-values

ADS 2E3

1E2

1E1

1

mpedance, Ohms

# A Common Design Guideline for 50 Years

27

University of Colorado, Boulder, ECEE

High Speed Digital Engineering Group

### The Reality Today

- Challenges in PDN design

- One example: rail collapse for I/O switching

- An homage to Bob Pease

- So what? good and not so good PCB layout strategies

- Legacy Code

30

• Final recommendations

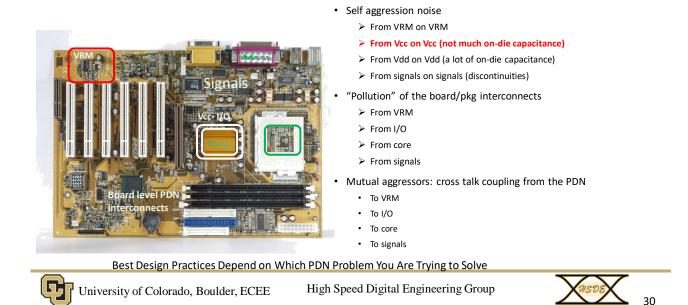

### Why PDN Design is so Confusing: It's not just 1 problem and root cause, it's 12

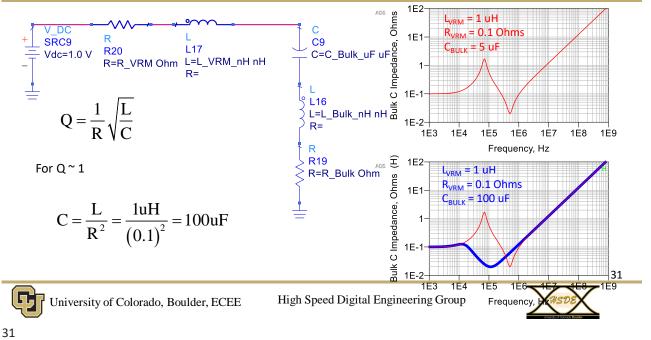

# Selecting the Bulk Decoupling Capacitor is about Managing the Parallel Resonance with the VRM Inductance

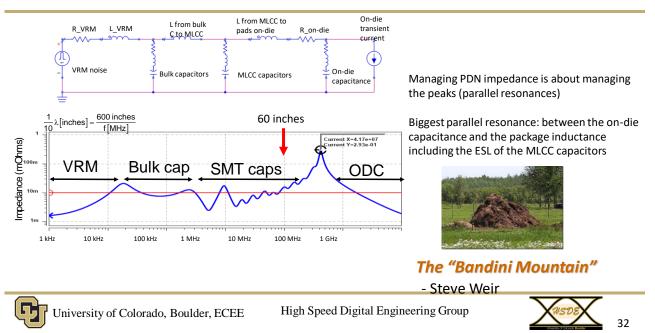

### PDN Design for the Core Rail is Dominated by Managing the Bandini Mountain

### Luck and Hope Should Not be Part of the Design Process

The faster you go, the less luck you seem to have

There is no substitute for applying good engineering principles

# Conclusion

- Interconnects will only add noise to your product

- Reduce noise by identifying potential problems and designing them out

- Base your designs on the root cause of the potential problems

- Turn the root cause into design guidelines

- There is no substitute to good engineering principles

### **Other Resources**

Sign up for complimentary 3-month subscription to the 200 hours of video training on the Signal Integrity Academy https://www.bethesignal.com/bogatin/3monthsubscription.php Use promo code: WEB23

Gj University of Colorado, Boulder, ECEE High Speed Digital Engineering Group

35